HBM高带宽内存走向与传统内存相当不同,后者依旧以提升I/O 传输时脉作为增加访问带宽的手段,HBM 则是以更宽的总线平行处理,单一堆栈采用1024bit,如今JEDEC 发布更新版JESD235B,同步提升容量与速度。

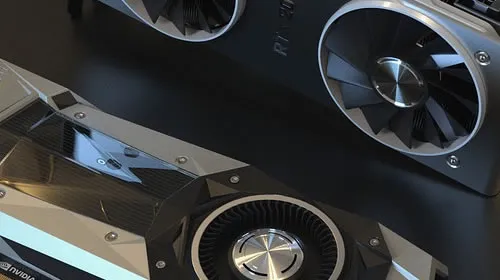

HBM(High Bandwidth Memory)高带宽内存对于计算机用户是个既熟悉又陌生的名词,在显卡领域仅有少数高端版本采用,却又对AI 深度学习、高性能运算、网络等需要高带宽、低功耗的应用环境提供不可或缺的性能表现。一般消费市场,最早由AMD Radeon R9 Fury/R9 Nano 显卡搭载HBM,由于HBM 采用interposer 与GPU 封装在同一基板(SiPs,system-in-packages),省去在电路板的内存布线,因此能够做出如Radeon R9 Nano 长度不到160mm 的身材。

HBM 单一堆栈采用 1024bit 总线宽度,以 8 个 128bit 独立信道所组成,可以堆栈 2~8 个内存晶粒,每个晶粒通过 TSV(Through Silicon Via)相互链接。每个晶粒可以提供 2Gb 容量,单一 pin 脚运行时脉为 500MHz,通过 DDR 技术完成 2 倍等效带宽 1Gbps,单一 HBM 堆栈即可完成 128GB/s 访问带宽。

HBM通过interposer 与其它具备内存控制器的晶粒相互链接,再封装至基板。 (图片取自AMD)

第二代HBM 单一堆栈总线宽度依旧是1024bit,由8 个128bit 信道所组成,但引进相当重要的Pseudo Channel mode,能够将128bit 拆成64bit+ 64bit 方式运行,这2 个64bit 信道共享命令信道,但内部bank 与I/O 数据信道则是相互分离,借此完成各自独立运行,能够减少访问延迟。此时也借由制程技术微缩,单一内存晶粒容量达到 8Gb,单一 pin 脚等效带宽拉高至 1.6Gbps~2Gbps。

近日JEDEC 再次针对HBM 规范JESD235 文件进行更新,JESD235B HBM 单一堆栈总线还是1024bit,但堆栈数量由2、4、8 层再往上加入4 层达12 层,单一内存晶粒容量顺势推升至16Gb,代表单一堆栈最大即可拥有24GB 容量。单一 pin 脚时脉如今采用 1200MHz,通过 DDR 技术完成 2.4Gbps 等效带宽。